Power Management IC For Embedded System

# **GERNAL DESCRIPTION**

DF1545 is a highly integrated power management IC (PMIC) designed for IPC,DVR,TV and consumer & multimedia applications. It offers a complete solution with minimum

component count, low power dissipation together with simple design. the DF1545 integrates 3- CH synchronous buck converter, 1- CH LDO, 1- CH reset monitor. The converters are optimized for high efficiency (greater than 92%) and feature integrated low impedance FETs.

# **FEATURES**

- Wide Input Voltage Range: 3.1V ~ 20V

High Efficient DC/DC Converter: 92~96%

Low Power Consumption (Sleep Mode ) < 10μA</li>

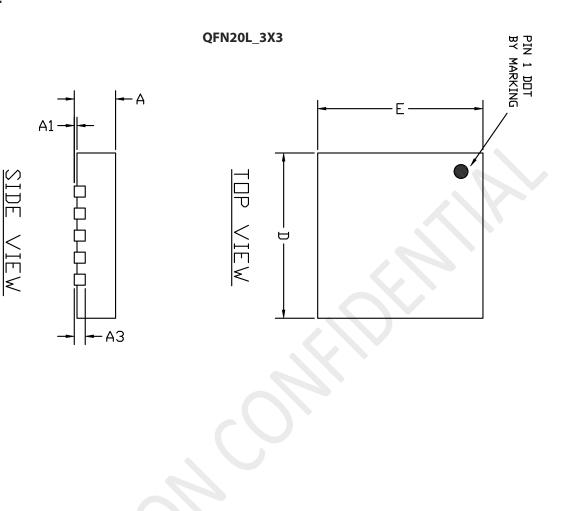

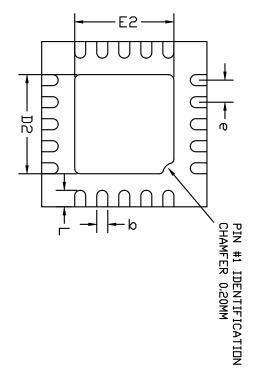

Integrate 4-CH Output in QFN20L-3X3 Package

- Buck DC/DC Converter (3-CH) HVBUCK1: Input 3.1V~20V, output 0.6V ~ VIN adjustable, load current up to 3A HVBUCK2: Input 3.1V~20V, output 0.6V~ VIN adjustable, load current up to 3A LVBUCK1: Input 2.5V~6V, output 0.6V~ VIN adjustable, load current up to 3A

- High PSRR LDO (1-CH) LDO:0.6V~5.0V adjustable, load current up to 1000mA.

- Reset Monitor (1-CH) provide a reset signal POR to the host processor with an external pull up voltage

- Protection

Over Voltage Protection (OVP)

Under Voltage Protection (UVP)

Over Current Protection (OCP)

Short Circuit Protection (SCP)

Over Thermal Protection (OTP)

# **APPLICATION**

- IPC

- DVR

- TV

1

## **PRODUCT OPTIONS**

| BLOCK           | INPUT VOLTAGE | OUTPUT VOLTAGE           | CAPABILITY                |

|-----------------|---------------|--------------------------|---------------------------|

| HVBUCK1/HVBUCK2 | 3.1~20V       | Adjustable               | Up to 3A                  |

| LVBUCK1         | 2.5~6V        | Adjustable               | Up to 3A                  |

| LDO             | 2.5V~6V       | Adjustable               | Up to 1000mA              |

| RESET MONITOR   | HVOUT2        | External pull up voltage | 100mS delay for Processor |

# **PIN CONFIGURATION**

## **PIN DESCRIPTIONS**

| PIN | NAME    | DESCRIPTION                                                                                                        |

|-----|---------|--------------------------------------------------------------------------------------------------------------------|

| 1   | HVBST1  | Bootstrap. A capacitor connected between HVSW1 and HVBST1 pins is required to                                      |

| I   | TIVDJII | form a floating supply across the high-side switch driver. Use a 22nF capacitor                                    |

| 2   | HVOUT1  | HVBUCK1 Feedback. Connect to the tap of an external resistor divider from the                                      |

| 2   |         | output to GND to set the output voltage.                                                                           |

| 3   | LVGP1   | Ground                                                                                                             |

| 4   | LVSW1   | LVBUCK1 Switching Pin, Connect this Pin to inductor, Minimize the track area to reduce EMI.                        |

| 5   | LVVP1   | LVBUCK1 Power supply Pin, Bypass 10µF capacitor to GND to reduce the input noise.                                  |

| 6   | LVOUT1  | LVBUCK1 Feedback. Connect to the tap of an external resistor divider from the                                      |

| 0   | LVOOTI  | output to GND to set the output voltage.                                                                           |

| 7   | LVEN1   | LVBUCK1 Enable (Active High) or Disable(Low or Floating).                                                          |

| 8   | FBLDO   | LDO Feedback. Connect to the tap of an external resistor divider from the output to GND to set the output voltage. |

| 9   | LDO     | LDO Output pin, Bypass 10µF capacitor to GND                                                                       |

| 10  | VPLDO   | LDO Power supply Pin, Bypass 10µF capacitor to GND to reduce the input noise.                                      |

| 11  | ENLDO   | LDO Enable (Active High) or Disable(Low or Floating).                                                              |

| 12  | POR     | Power On Reset                                                                                                     |

|     |         | HVBUCK2 Feedback. Connect to the tap of an external resistor divider from the                                      |

| 13  | HVOUT2  | output to GND to set the output voltage.                                                                           |

| 1.4 |         | Bootstrap. A capacitor connected between HVSW2 and HVBST2 pins is required to                                      |

| 14  | HVBST2  | form a floating supply across the high-side switch driver. Use a 22nF capacitor                                    |

| 15  | HVSW2   | HVBUCK2 Switching Pin, Connect this Pin to inductor, Minimize the track area to reduce EMI.                        |

| 16 | HVVP2 | HVBUCK2 Power supply Pin, Bypass 10µF capacitor to GND to reduce the input noise.           |

|----|-------|---------------------------------------------------------------------------------------------|

| 17 | HVEN2 | HVBUCK2 Enable (Active High) or Disable(Low or Floating).                                   |

| 18 | HVEN1 | HVBUCK1 Enable (Active High) or Disable(Low or Floating).                                   |

| 19 | HVVP1 | HVBUCK1 Power supply Pin, Bypass 10µF capacitor to GND to reduce the input noise.           |

| 20 | HVSW1 | HVBUCK1 Switching Pin, Connect this Pin to inductor, Minimize the track area to reduce EMI. |

| 21 | EP    | Thermal PAD, connect to Ground.                                                             |

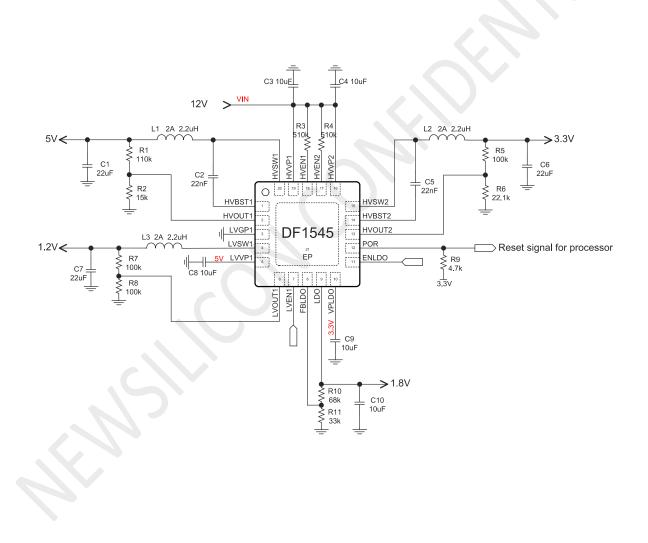

# **TYPICAL APPLICATIONS**

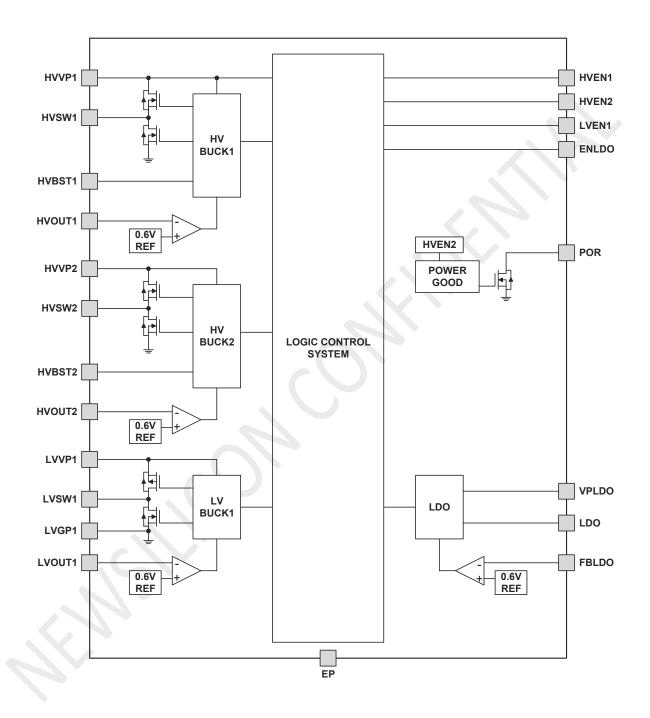

# SYSTEM BLOCK DIAGRAM

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                                           | MIN  | MAX     | UNIT |

|---------------------------------------------------------------------|------|---------|------|

| HVVP1,HVSW1,HVEN1                                                   | -0.3 | 30      | V    |

| HVVP2,HVSW2,HVEN2                                                   | -0.3 | 30      | V    |

| HVBST1,HVBST2                                                       |      | HVSWX+6 | V    |

| Other pin Voltage                                                   | -0.3 | 10      | V    |

| Junction Temperature                                                |      | 125     | °C   |

| Operating Temperature                                               | -40  | 125     | °C   |

| Storage Temperature Range                                           | -55  | 150     | °C   |

| Lead Temperature                                                    |      | 300     | °C   |

| Power Dissipation, P <sub>D</sub> @T <sub>A</sub> -25°C, QFN20L 3X3 |      | 2       | W    |

| HBM(Human Body Mode)                                                |      | 2       | kV   |

| MM(Machine Mode)                                                    |      | 200     | V    |

## ESD(electrostatic discharge) sensitive device.

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER         | MIN | MAX | UNIT |

|-------------------|-----|-----|------|

| HVVP1,HVSW1,HVEN1 | 3.1 | 20  | V    |

| HVVP2,HVSW2,HVEN2 | 3.1 | 20  | V    |

| Other pin Voltage | 2.5 | 6   | V    |

# **ELECTRICAL CHARACTERISTICS**

## **HVBUCK1 & HVBUCK2 Electrical Characteristics**

$(V_{IN} = 12V, T_A = 25^{\circ}C$  unless otherwise specified)

| PARAMETER                         | SYMBOL           | <b>TEST CONDITIONS</b>                | MIN   | ТҮР  | MAX   | UNIT |

|-----------------------------------|------------------|---------------------------------------|-------|------|-------|------|

| Input Voltage Range               | HVVP1/2          |                                       | 3.1   |      | 20    | V    |

| Input UVP Threshold               |                  | Input Voltage Falling                 |       |      | 3     | V    |

| Input OVP Threshold               |                  | Input Voltage Rising                  |       | 20   |       | V    |

| Standby Supply Current            |                  | HVOUTX= 103%,<br>I <sub>OUT</sub> = 0 |       | 400  | 600   | μΑ   |

| Shutdown Supply Current           |                  | HVENX = 0,<br>HVVPX = 12V             |       | 3    |       | μΑ   |

| EN Rising Threshold               | HVENX            | HVENX RISING                          |       | 1.4  |       | V    |

| EN Falling Threshold              | HVENX            | HVENX FALLING                         |       | 0.6  |       | V    |

| Feedback Voltage                  | HVOUTX           |                                       | 0.588 | 0.6  | 0.612 | V    |

| Output Voltage Line<br>Regulation |                  |                                       |       | 0.04 | 0.4   | %/V  |

| Output Voltage Load<br>Regulation |                  |                                       |       | 0.5  |       | %    |

| Current Limit                     | ILIM             | Duty = 30%                            |       | 3.5  |       | А    |

| Oscillator Frequency              | F <sub>sw</sub>  |                                       |       | 1.2  |       | MHz  |

| NMOS On Resistance                | R <sub>ONN</sub> | I <sub>sw</sub> =100mA                |       | 0.07 |       | Ω    |

### **LVBUCK1 Electrical Characteristics**

$(V_{IN} = 3.6V, T_A = 25^{\circ}C$  unless otherwise specified)

| PARAMETER           | SYMBOL | <b>TEST CONDITIONS</b> | MIN | ТҮР | MAX | UNIT |

|---------------------|--------|------------------------|-----|-----|-----|------|

| Input Voltage Range | LVVP1  |                        | 2.5 |     | 6   | V    |

| Input UVP Threshold |        | Input Voltage Falling  |     | 2.2 |     | V    |

| Input OVP Threshold |        | Input Voltage Rising   |     | 6.5 |     | V    |

NEWSILICON TECHNOLOGIES CO., LTD http://www.newsilicon.cn

| Operating Supply Current              |                  | LVOUT1= 60%,<br>I <sub>OUT</sub> = 0  |       | 150  | 200                 | μΑ  |

|---------------------------------------|------------------|---------------------------------------|-------|------|---------------------|-----|

| Standby Supply Current                |                  | LVOUT1= 103%,<br>I <sub>OUT</sub> = 0 |       | 40   | 80                  | μΑ  |

| Shutdown Supply Current               |                  | $LVEN1 = 0, V_{IN} = 4.2V$            |       | 0.1  | 1                   | μΑ  |

| EN Rising Threshold                   | LVEN1            | LVEN1 Rising                          |       | 1.4  |                     | V   |

| EN Falling Threshold                  | LVEN1            | LVEN1 Falling                         |       | 0.6  |                     | V   |

| Output Voltage Regulation<br>Accuracy | LVOUT1           |                                       | -1.5  | 1    | 1.5                 | %   |

| Feedback Voltage                      |                  |                                       | 0.588 | 0.6  | 0.612               | V   |

| Output Voltage Line<br>Regulation     |                  |                                       |       | 0.04 | 0.4                 | %/V |

| Output Voltage Load<br>Regulation     |                  |                                       |       | 0.5  | $\langle N \rangle$ | %   |

| Current Limit                         | I <sub>LIM</sub> | Duty = 30%                            |       | 3.5  |                     | А   |

| Oscillator Frequency                  | F <sub>sw</sub>  |                                       |       | 1.2  |                     | MHz |

| PMOS On Resistance                    | R <sub>ONP</sub> | I <sub>sw</sub> =100mA                |       | 0.1  |                     | Ω   |

| NMOS On Resistance                    | R <sub>ONN</sub> | I <sub>sw</sub> =100mA                |       | 0.07 |                     | Ω   |

### LDO Electrical Characteristics

#### $(V_{IN} = 3.6V, T_A = 25^{\circ}C$ unless otherwise specified)

| VIN = 5.0V, TA = 25 C unicss otherwise specified, |                    |                       |       |     |       |      |  |  |  |

|---------------------------------------------------|--------------------|-----------------------|-------|-----|-------|------|--|--|--|

| PARAMETER                                         | ARAMETER SYMBOL TE |                       |       | ТҮР | MAX   | UNIT |  |  |  |

| Input Voltage Range                               | VPLDO              |                       | 2.5   |     | 6     | V    |  |  |  |

| Input UVP Threshold                               |                    | Input Voltage Falling |       | 2.2 | 2.5   | V    |  |  |  |

| EN Rising Threshold                               | ENLDO              | ENLDO Rising          |       | 1.4 |       | V    |  |  |  |

| EN Falling Threshold                              | ENLDO              | ENLDO Falling         |       | 0.6 |       | V    |  |  |  |

| Output Voltage Accuracy                           |                    |                       | -3    | 1.5 | 3     | %    |  |  |  |

| Feedback Voltage                                  | FBLDO              |                       | 0.588 | 0.6 | 0.612 | V    |  |  |  |

### **RESET MONITOR Electrical Characteristics**

$(V_{PULLUP} = 3.3V, T_A = 25^{\circ}C \text{ unless otherwise specified})$

| PARAMETER     | SYMBOL             | TEST CONDITIONS M            |    | ТҮР | MAX | UNIT |

|---------------|--------------------|------------------------------|----|-----|-----|------|

| POR threshold | V <sub>OUT2</sub>  | V <sub>OUT2</sub> rising     | 85 | 90  | 95  | %    |

| Delay time    | T <sub>delay</sub> | Delay before POR<br>released |    | 100 |     | ms   |

## **GENERAL DESCRIPTION**

#### **Feature Description**

DF1545 is a highly efficient and integrated Power Management IC for analog and digital satellite receivers. The device incorporates 3 high-efficiency synchronous buck regulators and 1 LDO that deliver 4 output voltages. The device also includes a reset monitor that provides a reset output signal for processor.

Each of the buck regulators is specially designed for high-efficiency operation throughout the load range. With 1.2MHz typical switching frequency, the external L- C filter can be small and still provide very low output voltage ripple. The bucks are internally compensated to be stable with the recommended external inductors and capacitors as detailed in the application diagram. Synchronous rectification yields high efficiency for low voltage and high output currents.

Additional features include soft-start, under-voltage protection, over-voltage protection, short-current protection, over-current protection and thermal overload protection. All BUCKs can operate in automatic mode (PWM/PFM). At very light loads, BUCKs enter PFM mode and operate with reduced switching frequency and supply current to maintain high efficiency.

### Soft start

Each of converters has an internal soft-start circuit that limits the in-rush current during startup. This allows the converters to gradually reach the steady-state operating point, thus reducing startup

stresses and surges. During startup, the switch current limit is increased in steps. For BUCKs the soft start is implemented by increasing the switch current limit in steps that are gradually set higher. The startup time depends on the output capacitor size, load current and output voltage.

### **Current Limiting**

A current limit feature protects the device and any external components during overload conditions. In PWM mode the current limiting is implemented by using an internal comparator that trips at current levels according to the buck capability. If the output is shorted to ground the device enters a timed current limit mode where the NFET is turned on for a longer duration until the inductor current falls below a low threshold, ensuring inductor current has more time to decay, thereby preventing runaway.

### **Startup Sequence**

Once HVVP1/HVVP2/LVVP1/VPLDO reaches the UVP threshold and the ENABLE pin= High the HVBUCK1/HVBUCK2/LVBUCK1/LDO will start up.

### **Reset Monitor**

The POR pin of DF1545 is an open-drain output between the POR pin and the GND pin. The power on reset output asserts low until the output voltage on the HVOUT2 pin exceeds the setting thresholds (91%) and the deglitch timer(100ms) has expired. Additionally, whenever the HVEN2 pin is low or open, POR immediately asserts low regardless of the output voltage.

When the POR is released (not asserted low) an external resistor connected to any external bias voltage pulls up this POR pin.

## Under Voltage Protection (UVP)

HVVP1/HVVP2/LVVP1/VPLDO voltage is monitored for a supply under voltage condition, for which the operation of the device cannot be guaranteed. The

# **Detailed Design Procedure**

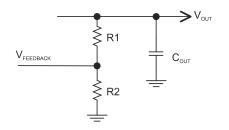

## **Adjusting the Output Voltage**

For HVBUCK1/HVBUCK2/LVBUCK1/LDO, A resistor divider from the output node to the feedback pin sets the output voltage. recommends using 1% tolerance or better divider resistors. Start with fixed value for the R1 resistor and use Equation to calculate R2.

To improve efficiency at light loads, consider using larger-value resistors. If the values are too high, the regulator is more susceptible to noise, and voltage errors from the feedback input current are noticeable. part will automatically disable. To prevent unstable operation, the UVP has a hysteresis window. Each under voltage protection (UVP) will disable it's outputs, Once the supply voltage is above the UVP hysteresis, the device will initiate a power-up sequence and then enter the active state.

## **Over Voltage Protection (OVP)**

HVVP1/HVVP2/LVVP1 voltage is monitored for a supply over voltage condition, for which the operation of the device cannot be guaranteed. The purpose of OVP is to protect the part and all other components connected to the PMIC outputs from any damage and malfunction. Once HVVP1/HVVP2 rises over about 20V, HVBUCK1/HVBUCK2 will be disabled automatically. To prevent unstable operation, the OVP has a hysteresis window. An over voltage protection (OVP) will force the device into the reset state, Once the supply voltage goes below the OVP lower threshold, the device will initiate a power-up sequence and then enter the active state. HVBUCK1/HVBUCK2 operating maximum input voltage at which parameters are guaranteed is 20V. Absolute maximum of the device is 30 V.

## Thermal Shutdown(OTP)

The temperature of the silicon die is monitored for an over-temperature condition, for which the operation of the device cannot be guaranteed. The part will automatically be disabled if the temperature is too high. The thermal shutdown (OTP) will force the device into the reset state. In reset, all circuitry is disabled. To prevent unstable operation, the OTP has a hysteresis window of about 20°C. Once the temperature has decreased below the OTP hysteresis, the device will initiate a power-up sequence and then enter the active state. In the active state, the part will start up as if for the first time.

$V_{OUT} = V_{FEEDBACK} \times \frac{R1 + R2}{R2}$

Select R1 value then

R2=R1×

$$rac{V_{FEEDBACK}}{V_{OUT}}$$

-V<sub>FEEDBACK</sub>

Where VFEEDBACK=0.6V

NEWSILICON TECHNOLOGIES CO.,LTD http://www.newsilicon.cn REV1.0

### **BUCK Power Supply Recommendations**

HVBUCK1/HVBUCK2 input voltage supply range is between 3.1 V and 20V.

LVBUCK1 input voltage supply range is between 2.5 V and 6V

This input supply must be well regulated. If the input supply is located more than a few inches, additional bulk capacitance may be required in addition to the ceramic bypass capacitors. An electrolytic capacitor with a value of 47uF is a typical choice.

HVVP1/HVVP2/LVVP1/VPLDO must all be connected to input capacitors as close as possible.

#### **BUCK Inductor Selection**

Use a 1µH-to-10µH inductor with a DC current rating of at least 25% percent higher than the maximum load current for most applications. For highest efficiency, select an inductor with a DC resistance less than 15m $\Omega$ . For most designs, derive the inductance value from the following equation.

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_L \times F_S}$$

Where  $\Delta I_L$  is the inductor ripple current. Choose an inductor current approximately 30% of the maximum load current. The maximum inductor peak current is:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_L}{2}$$

Under light-load conditions (below 100mA), use a larger inductor to improve efficiency.

#### **BUCK Input Capacitor Selection**

The input current to the step-down converter is discontinuous, and therefore requires a capacitor to both supply the AC current to the step-down converter and maintain the DC input voltage. For the best performance, use low ESR capacitors, such as ceramic capacitors with X5R or X7R dielectrics and small temperature coefficients. A 22µF capacitor is sufficient for most applications. The input capacitor requires an adequate ripple current rating because it absorbs the input switching. Estimate the RMS current in the input capacitor with:

$$I_{CIN} = I_{LOAD} \times \frac{\sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}}{V_{IN}}$$

The worst-case condition occurs at VIN = 2VOUT, where:

$I_{CIN} = \frac{I_{LOAD}}{2}$

For simplification, choose an input capacitor with an RMS current rating greater than half the maximum load current. The input capacitor can be electrolytic, tantalum, or ceramic. Place a small, high-quality, ceramic capacitor ( $0.1\mu$ F) as close to the IC as possible when using electrolytic or tantalum capacitors. When using ceramic capacitors, make sure that they have enough capacitance to provide sufficient charge to prevent excessive input voltage ripple. Estimate the input voltage ripple caused by the capacitance with:

$$\Delta V_{IN} = \frac{I_{LOAD}}{F_S \times C_{IN}} \times \frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

## **BUCK Output Capacitor Selection**

The output capacitor maintains the DC output voltage. Use ceramic, tantalum, or low-ESR electrolytic capacitors. Use low ESR capacitors to limit the output voltage ripple. Estimate the output voltage ripple with:

$$\Delta V_{OUT} = \frac{V_{OUT}}{F_{S} \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times \left(R_{ESR} + \frac{1}{8 \times F_{S} \times C_{OUT}}\right)$$

Where L is the inductor value and RESR is the equivalent series resistance (ESR) of the output capacitor.

For ceramic capacitors, the capacitance dominates the impedance at the switching frequency and causes most of the output voltage ripple. For simplification, estimate the output voltage ripple with:

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 \times F_{S}^{2} \times L \times C_{OUT}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

For tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated with:

$$\Delta V_{OUT} = \frac{V_{OUT}}{F_{S} \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times R_{ESR}$$

The characteristics of the output capacitor also affect the stability of the regulation system. The DF1545 can be optimized for a wide range of capacitance and ESR values.

### **BUCK Bootstrap Capacitor Selection**

Connect a 22nF ceramic capacitor between the HVBST1/HVBST2 and HVSW1/HVSW2 pins for proper operation.recommends using a ceramic capacitor with X5R or better-grade dielectric. The capacitor should have a 6.3V or higher voltage rating.

### **LDO Output Capacitor Selection**

The LDO is designed to be stable with a minimum  $4.7\mu$ F output capacitor. No series resistor is required when using low ESR capacitors. For most applications, a  $10\mu$ F ceramic capacitor is recommended. Larger values will improve transient response, and raise the power supply rejection ratio (PSRR) of the LDO. Refer to the Typical Performance Characteristics for the allowable range of output capacitor to ensure loop stability.

### **Layout Guidelines**

PC board layout is an important part of DC-DC converter design. Poor board layout can disrupt the performance of a DC-DC converter and surrounding circuitry by contributing to EMI, ground bounce, and resistive voltage loss in the traces. These can send erroneous signals to the DC-DC converter resulting in poor regulation or instability. Good layout can be implemented by following a few simple design rules.

1. Minimize area of switched current loops. In a buck regulator there are two loops where currents are switched rapidly. The first loop starts from the CIN input capacitor, to the regulator VIN terminal, to the regulator SW terminal, to the inductor then out to the output capacitor COUT and load. The second loop starts from the output capacitor ground, to the regulator GND terminals, to the inductor and then out to COUT and the load. To minimize both loop areas the input capacitor should be placed as close as possible to the VIN terminal. Grounding for both the input and output capacitors should consist of a small localized top side plane that connects to GND. The inductor should be placed as close as possible to the SW pin and output capacitor.

2. Minimize the copper area of the switch node. The SW terminals should be directly connected with a trace that runs on top side directly to the inductor. To minimize IR losses this trace should be as short as possible and with a sufficient width. However, a trace that is wider than 100 mils will increase the copper area and cause too much capacitive loading on the SW terminal. The inductors should be placed as close as possible to the SW terminals to further minimize the copper area of the switch node. 3. Have a single point ground for all device analog grounds. The ground connections for the feedback components should be connected together then routed to the GND pin of the device. This prevents any switched or load currents from flowing in the analog ground plane. If not properly handled, poor grounding can result in degraded load regulation or erratic switching behavior.

4. Minimize trace length to the FB terminal. The feedback trace should be routed away from the SW pin and inductor to avoid contaminating the feedback signal with switch noise.

5. Make input and output bus connections as wide as possible. This reduces any voltage drops on the input or output of the converter and can improve efficiency. If voltage accuracy at the load is important make sure feedback voltage sense is made at the load. Doing so will correct for voltage drops at the load and provide the best output accuracy.

PACKAGE

| P        | ES   | DS   |      | q    | ED   | D    | A3        | A1   | A    | REF. | PKG.        |                       |  |

|----------|------|------|------|------|------|------|-----------|------|------|------|-------------|-----------------------|--|

|          | 1.65 | 1.65 | 0.25 | 0,15 | 2,95 | 2,95 |           | 0,00 | 0,70 | MIN. | ∕ : V       | COMMON DIM            |  |

| 0,40 BSC | 1,80 | 1.80 | 0,30 | 0,20 | 3,00 | 3,00 | 0.20 REF. | 1    | 0,75 | NDM. | WIVERY VERY | COMMON DIMENSIONS(MM) |  |

|          | 1.90 | 1.90 | 0,35 | 0,25 | 3,05 | 3,05 |           | 0,05 | 0.80 | MAX  | THIN        |                       |  |

NEWSILICON TECHNOLOGIES CO.,LTD http://www.newsilicon.cn REV1.0